## MINIATURIZED REVERSE MODULATION LOOP FOR A CQPSK 120-Mbit/s MODEM\*

K. K. Ralston, \*\* R. K. Gupta, F. T. Assal, and R. T. Kroll

COMSAT Laboratories, Clarksburg, Maryland 20871-9475

### Abstract

The design and performance of a miniaturized reverse modulation loop (RML) for carrier recovery in a 120-Mbit/s coherent quadrature phase shift keying (CQPSK) modem for on-board satellite applications are presented. The RML circuit, consisting of a modulator, demodulator, and comparator circuit, has been fabricated using quasi-monolithic techniques with dimensions of  $1.65 \times 4$  cm. The relative phase for all four states of the modulator is in close agreement with design values of  $90^\circ \pm 1^\circ$  over a 200-MHz bandwidth at 3.95 GHz. The demodulator and comparator circuits of the RML have successfully recovered a 120-Mbit/s bit stream.

### INTRODUCTION

Future communications satellite configurations are envisioned to include multibeam phased-array antennas, on-board signal regeneration, and switching at baseband and microwave frequencies (1). On-board demodulation and remodulation of digitally modulated signals in communications satellites offer substantial link-budget advantages because of the separation of up-link and down-link bit error rate (BER) performance characteristics (2). Coherent quadrature phase shift keying (CQPSK) modems, which require carrier recovery on board the satellite, offer a potential 2.5-dB performance advantage over differential detection schemes (3). This advantage may be used to improve transmission quality, reduce earth station size, increase the data throughput rate, or reduce the satellite's effective isotropically radiated power (e.i.r.p.). A second advantage of coherent systems is the avoidance of one-symbol time delays (16.6 ns in a 120-Mbit/s system) (4), thus reducing the size of the delay element and the modem. However, additional hardware, in the form of a very stable voltage-controlled oscillator (VCO), is necessary for carrier recovery in a CQPSK repeater (4), (5). One of the key requirements for on-board satellite application of CQPSK modem technology is the development of lightweight, power-efficient hardware with high reliability.

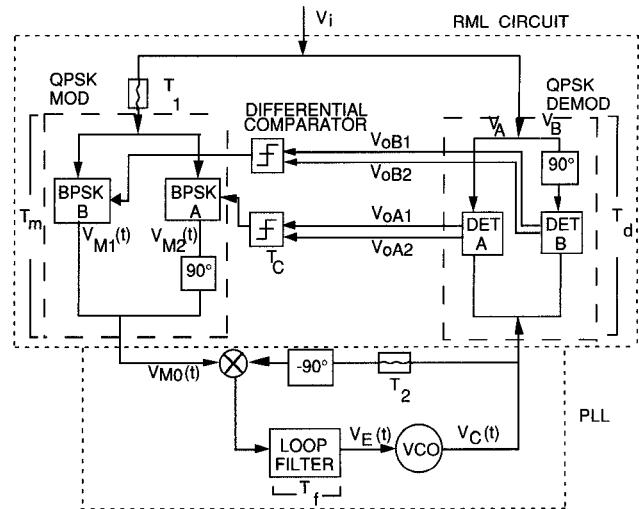

The RML method of implementing the carrier recovery portion of a CQPSK modem (Figure 1) uses less hardware than the fourth-power method (5) because it requires neither coherent frequency translation for narrowband filtering nor RF amplification. Furthermore, it does not need the baseband multipliers used in the Costas loop (6). An added advantage of an RML design is that the circuit can be fabricated entirely with monolithic microwave integrated circuit (MMIC) technology, resulting in decreased size and increased reliability. In addition, the RML design recovers the data as part of the carrier recovery process. However, the time delays (7) in the RML circuit are very critical, and any errors in the time delays through the RML can adversely affect the associated BER and the rate of cycle slippage (8). The

absolute delays through the RML can be compensated and do not adversely affect the loop parameters discussed above. Longer delay line lengths are expected to produce larger errors because of line length uncertainties and variations due to temperature. Therefore, these RF delays should be reduced by circuit miniaturization and by minimizing baseband delays.

This paper presents the design and performance of a miniaturized RML circuit for carrier and data recovery in a 120-Mbit/s modem. Key features of this circuit include significant size reduction and reliability enhancement by monolithic integration of resistors and capacitors on an alumina substrate, and performance enhancement by minimizing time delays in the RF and the comparator circuits.

### CIRCUIT DESIGN AND FABRICATION

The three basic sections of an RML circuit are the demodulator, the comparator, and the modulator (Figure 1). The demodulator is used to recover in-phase and quadrature (I and Q) bit streams. These data are then hard-limited and inverted by a digital comparator. The data are used to modulate the delayed modulated signal from which they were recovered, yielding the carrier. The correct operation of this system depends on synchronizing the modulated carrier, the data, and a locally generated carrier by using an additional phase-locked loop (PLL). Miniaturization of the RML circuit reduces delays, thereby improving performance by minimizing time delay variations.

Figure 1. Reverse Modulation Loop System Showing Time Delays

\*This paper is based on work performed at COMSAT Laboratories under the sponsorship of the Communications Satellite Corporation.

\*\*Currently at the University of Wisconsin, Madison, Wisconsin.

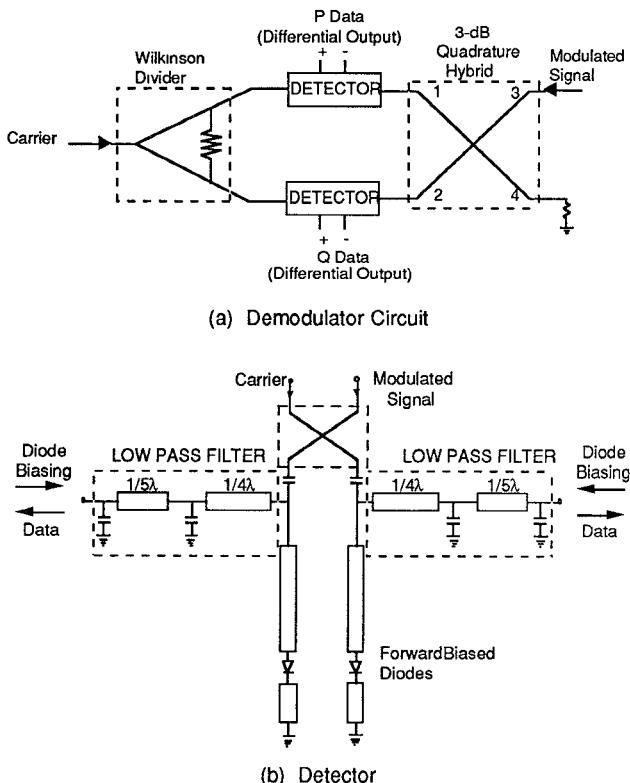

Figure 2a is a block diagram of the demodulator. The carrier enters the demodulator through a Wilkinson divider and is split evenly between two detectors. Similarly, the modulated carrier is split by the 3-dB quadrature hybrid and enters the other detector port. The detector (Figure 2b) uses diode mixers and low-pass filters to extract data from the modulated carrier. The mixer design uses a pair of forward-biased Schottky diodes and a quadrature hybrid. Each detector has two complementary outputs, which are passed through low-pass filters and reshaped by the comparator circuit. The filters also function as bias lines for the diodes, eliminating the need for an extra bias network. The low-pass filter, implemented with an inductance capacitance (LC) network, is designed with a cutoff frequency of 1 GHz and a flat group delay. The filter provides greater than 30-dB rejection for frequencies greater than 2 GHz.

The circuits were designed and modeled using the SuperCompact™ and Touchstone™ computer-aided-design (CAD) packages. Appropriate changes were made to the computer model to include discontinuities such as bends and junctions, as well as coupling between the lines. Wherever possible, narrow transmission lines with higher inductance per unit length and smaller line spacing were used to make the circuit compact. The circuits were designed to be highly symmetrical in order to reduce the effects of noise and minimize the effects of fabrication tolerances.

The comparator circuit consists of a gallium arsenide (GaAs) integrated circuit (IC) chip and an alumina substrate with printed lines and resistors for the required inputs and outputs. A Gigabit Logic dual differential amplifier (10G012B) was selected for comparator applications. This IC is designed to operate at frequencies up to 1.75 GHz with an average propagation delay of 375 ps. The 1.3 x 1.75-mm chip is mounted in die form to minimize the overall circuit size. In the RML circuit, the propagation delay through the compara-

Figure 2. Circuit Diagram of the RML Demodulator

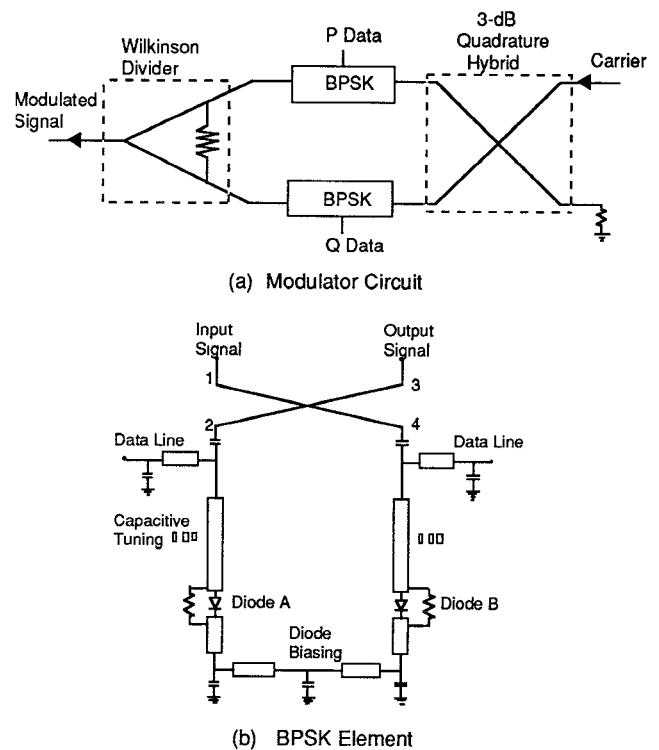

Figure 3. Circuit Diagram of the RML Modulator

tor circuit must be compensated by RF delays in the RML circuit. The comparator delay of 0.375 ns, compared to 3 ns for emitter-coupled logic (ECL) (5), results in a significant reduction in the size of the delay lines and the modem.

A resistive network, which can be adjusted in discrete increments, at the differential amplifier input provides the DC bias for the demodulator diodes. These diodes require a bias between -0.2 and -0.45 V to operate in the square law region. At the comparator output, pull-up resistors provide a termination for the open emitter of the amplifiers, and the series resistors act as current limiters to protect the modulator circuit. Only one comparator output is used for switching the modulator; the second may be used in the modem clock recovery circuit. The variable threshold control resistor network allows the threshold switching voltage to be adjusted for interfacing to ECL voltage levels. Both the threshold voltage and the DC bias for the demodulator diodes should be identical for good common-mode rejection of incoming signals. Large, discrete shunt capacitors (~500 pF) connected between the power supply voltages and ground prevent transient voltage spikes from interfering with the data.

The modulator (Figure 3a) uses a quadrature hybrid to split the incoming signal into two signals 90° out of phase. Each signal is modulated in a binary phase shift keying (BPSK) circuit with the I and Q data streams from the comparator. The two BPSK outputs are then recombined by an in-phase Wilkinson divider to yield the carrier. The BPSK circuit (Figure 3b) is a reflection-type design with diodes acting as virtual shorts or opens to give the required phase shift between states. A resistor network parallel to each diode is designed to compensate for the finite on-state resistance of the Schottky diodes and provide the desired amplitude balance between the states. The Schottky diode has a forward resistance of  $\sim 15 \Omega$ , which corresponds to a reflection loss of approximately 2.7 dB. Schottky diodes are preferable to PIN diodes in this design because of their small control signal power, simpler design, and faster switching time. The

Hewlett-Packard HP2082-2716 Schottky diode, and its more recent version, the HSC5314, were selected for this application. The diode model used to design the BPSK circuit was based on characterization and testing for HP2082-2716 diodes (9). The data lines, DC blocking capacitors, and diode control lines were included in the LC phase-matching network used to compensate for the finite package reactance of the diodes and to provide the necessary  $180^\circ$  phase shift between states.

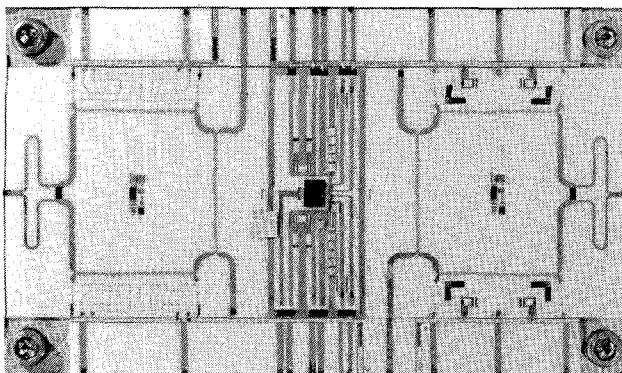

Figure 4 is a photograph of the circuit, which has overall dimensions of  $1.65 \times 4$  cm. The RML circuit was fabricated using a quasi-monolithic approach in which the passive elements are deposited on a substrate using MMIC fabrication techniques, and discrete active devices are then selected and mounted in the circuit. In addition, thin-film resistors and metal-insulator-metal (MIM) capacitors were used wherever possible to make the layout compact. Air bridges were used in the quadrature hybrids instead of bondwires. A substrate height of 15 mil was selected to allow wider lines for the quadrature hybrid design. The line widths and spacing in the hybrid are critical to its operation. Wider lines provide less circuit performance sensitivity to fabrication uncertainties. Minimum 30- $\mu$ m hybrid line widths and spacings were used. This minimum dimension limited any errors to  $\pm 10$  percent of the modeled value due to fabrication uncertainties. Realization of the RML circuit on a single substrate, and reduction of the number of discrete components, should increase circuit reliability while reducing the length of interconnection lines and circuit assembly time.

Figure 4. The Reverse Modulation Loop (dimensions:  $1.65 \times 4$  cm)

### MEASURED RESULTS

The three sections of the RML were tested individually using an aluminum test fixture designed to test the performance of the RML circuit components. The RML circuit was epoxied to a Kovar test carrier which can be mounted in the test fixture. A metal ridge was used on the carrier to provide ground connections for the entire circuit. Alumina distribution boards were employed so that the circuit could easily be assembled and removed from the test fixture.

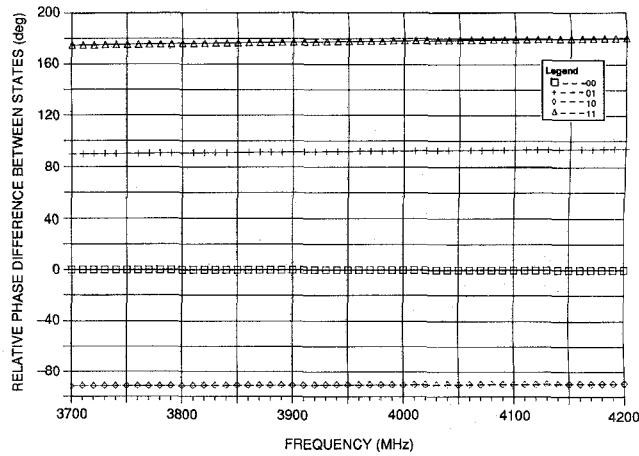

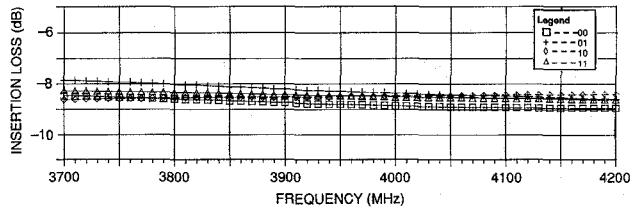

The modulator was tested in the static mode with an HP8510 network analyzer system for amplitude and phase balance. The measured relative phase difference between the four modulator states (Figure 5) was in close agreement with modeled values of  $90^\circ \pm 1^\circ$  over a 200-MHz bandwidth at 3.95-GHz center frequency. The average modulator insertion loss (Figure 6) was 8.4 dB, 0.8 dB higher than the predicted values. This could be caused by fixture and RF connector losses. The amplitude balance was within  $\pm 0.3$  dB, and the input and output return losses were better than 20 dB across the frequency band of operation. Dynamic measurements of the modula-

Figure 5. Measured Phase Difference Between Modulator States

Figure 6. Insertion Loss for Modulator States

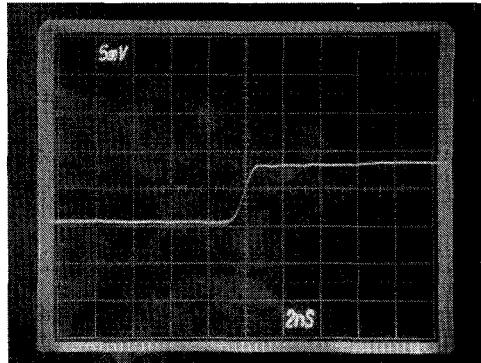

Figure 7. Transient Response of the Modulator

tor were performed by mixing the output of the modulator with a carrier and observing the resulting data on an oscilloscope. The modulator rise time of 1.4 ns (Figure 7) was measured by observing the transient response for a single bit, which made it possible to operate the modulator at bit rates higher than 120 Mbit/s.

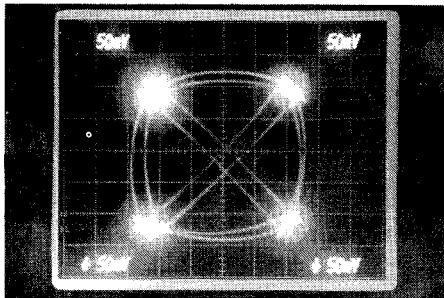

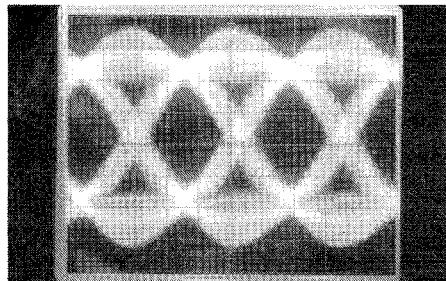

Measurements were made on the demodulator to determine the phase balance between all four states. For these measurements, the detected outputs were applied to horizontal and vertical traces of an oscilloscope. To check the demodulator's response during state transitions, a low-speed (8-kHz) random bit pattern was modulated on a carrier and detected with the demodulator. As shown in Figure 8, the transitions between the four phase states (represented by the lines between the corner points) are clean. The blurring at the corners represents a return to the same state in successive bits, and the associated transients. The eye pattern shown in Figure 9 was generated for each detector by viewing the detected data on an oscilloscope for a random  $2^{23} - 1$  bit pattern. The resulting steady-state pattern also shows smooth transitions between states, an open eye shape, and focused data points.

Figure 8. Phase Balance and Transient Response of the Demodulator

Figure 9. Eye Pattern for the Demodulator Detector

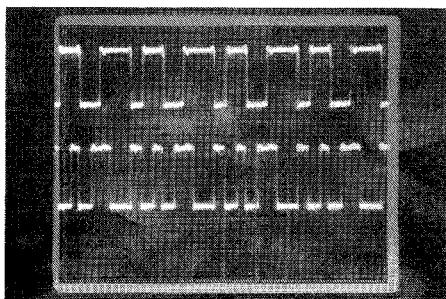

The comparator circuit was independently tested by simulating the input from the demodulator with a pulse generator. These tests showed that the circuit could be operated well with input levels of 100 mV. The comparator circuit was also tested with detected signals from the demodulator as its inputs. The demodulator produced an output level of 25 to 75 mV into a  $50\Omega$  load. A resistance value of  $175\Omega$  was used in the final comparator circuit to raise the demodulator output voltage. The comparator pull-up resistors used for biasing the detector diodes and the threshold resistor were adjusted for a diode bias voltage of  $-0.45$  V to maximize the demodulated data amplitude. The comparator outputs for both I and Q data streams were then observed for several 16-bit words, as shown in Figure 10. For modulated signal and clean carrier power levels of 1.8 and 1.2 dBm, respectively, the comparator output voltage was 0.5 V for a detected bit.

Figure 10. Comparator Outputs for Different Data Patterns

## CONCLUSIONS

A miniaturized RML circuit has been designed and fabricated using a quasi-monolithic approach, which results in small size and enhanced circuit reliability. Miniaturization of the demodulator, comparator, and modulator circuits permits their implementation on a single substrate. The amplitude and phase balance of the modulator are close to the design goals. The demodulator and comparator were demonstrated to successfully recover data at 120 Mbit/s. These results show that the RML circuit is capable of integration in a miniaturized 120-Mbit/s CQPSK modem.

## ACKNOWLEDGMENTS

The authors wish to acknowledge the efforts of J. Kearney, L. Pryor, and J. Tyler during design, layout, fabrication, and assembly of these circuits. They also wish to thank C. Cotner of Intelsat Satellite Services, COMSAT World Systems Division, and C. Fonstad of MIT for their support and encouragement.

## REFERENCES

- (1) C. Mahle, G. Hyde, and T. Inukai, "Satellite Scenarios and Technology for the 1990s," *IEEE Journal on Selected Areas in Communications*, Vol. SAC-5, No. 4, May 1987, pp. 556-570.

- (2) S. J. Campanella, F. T. Assal, and A. L. Berman, "Onboard Regenerative Repeater," *IEEE International Conference on Communications*, Chicago, June 1977, *Conf. Rec.*, pp. 6.2-121-6.2-125.

- (3) K. Feher, *Digital Communications, Satellite Earth Stations Engineering*, Englewood Cliffs, New Jersey: Prentice-Hall, 1981, p. 184.

- (4) W. H. Childs *et al.*, "A 120-Mbit/s 14-GHz Regenerative Receiver for Spacecraft Applications," *COMSAT Technical Review*, Vol. 11, No. 1, Spring 1981, pp. 103-130.

- (5) R. G. Egri, K. Karimullah, and F. T. Assal, "A 120-Mbit/s TDMA QPSK Modem for On-Board Applications," *COMSAT Technical Review*, Vol. 17, No. 1, Spring 1987, pp. 23-54.

- (6) James J. Spilker, *Digital Communications by Satellite*, Englewood Cliffs, New Jersey: Prentice-Hall, 1977, pp. 302-315, 390-397.

- (7) H. Yamamoto, K. Hirade, and Y. Watanabe, "Carrier Synchronizer for Coherent Detection of High-Speed Four-Phase-Shift-Keyed Signals," *IEEE Transactions on Communications*, Vol. COM-20, No. 4, August 1972, pp. 803-808.

- (8) K. K. Ralston, "Miniaturized Reverse Modulation Loop for a CQPSK 120 Mbit/s Modem," B.S./M.S. Thesis, Massachusetts Institute of Technology, Cambridge, Massachusetts, August 1989, pp. 36-43.

- (9) K. Karimullah and R. G. Egri, "A 4-GHz QPSK Modulator for High Bit Rates," *COMSAT Technical Review*, Vol. 15, No. 2A, Fall 1985, pp. 197-210.